1. Introduction

FPGA入门教程。

本文只讲如果在zedboard上运行linaro,不深讲原理,只讲操作。

2. 环境

2.1 硬件环境

using the Xilinx Zynq®-7000 All Programmable SoC.

AES-Z7EV-7Z020-G

REV-D版本(!!始终没有弄好图形界面!!)

2.2 软件环境

Vivado 2016.4

Xilinx SDK 2016.4

Debian 9 x86_64

交叉编译器用vivado自带的arm-xilinx-linux-gnueabi-

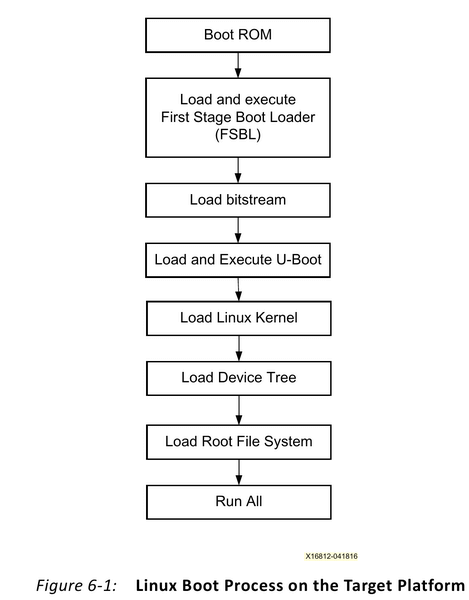

3. 系统启动流程

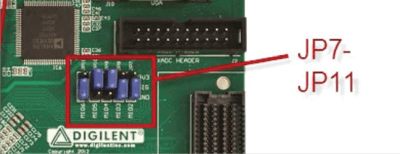

电源打开后,CPU0会执行已经写死在板子上BootROM中的程序,程序会根据JP7-JP11的设定状态来更新状态寄存器。

如上的状态表示从SD卡启动。还有NOR Flash、JTAG 等方式。

- 如果是SD卡模式启动,那么它会读取sd卡的第一分区,寻找

boot.bin(不分大小写)文件。该文件包含了FSBL( First Stage Boot Loader)程序,它接管CPU。CPU0会将该程序复制到内部256KB的片上内存中,并执行FSBL,进入下一个阶段。 - FSBL初始化DDR内存,GPIO等,接下来载入放在

boot.bin中的位元流(bitstream),用它来对可编程逻辑区块(Programmable Logic, PL)进行设定,板子的蓝灯将亮起来(如果在制作boot.bin文件时没有添加bitstream,那么蓝灯不会亮,PL也没有设定,只是在跑arm)。 - CPU将交给

boot.bin中的下一部分接管,可以是用户自己的程序(Note.1),或者是SSBL(Second Stage Boot Loader)。 - 如果SSBL是uboot,它可以做一些准备工作之后启动linux 内核(或者用户程序),可以再继续引导启动sd卡第二个分区的系统,比如linaro-ubuntu。

几种开发模式:

| 开发模式 | 解释 |

|---|---|

| 纯PL开发 | |

| 纯PS开发 | 典型的demo helloword |

| PS+PL(无OS) | 没有操作系统,生成的elf文件包括了硬件配置信息(xmp)和裸跑的C程序。包含bit文件 |

| PS+PL(含OS) | 包含boot.bin(boot.elf, your_bitstream.bit, fsbl.elf),devicetree.dtb,linux内核镜像,文件系统 |

本文介绍的构建系统,属于上述表格中的最后一种。

我们需要的东西有:Boot.bin,devicetree.dtb, uboot,rootfs。

rootfs(文件系统),我们有两种选择:

- ramdisk: 非常小,几乎没什么功能,运行在ram里,任何修改在重启之后就会丢失

- 完整的Linux文件系统,比如Linaro Ubuntu

4. 准备SD卡

分成两个主分区

- FAT32格式,>= 50MB

- ext4格式,>= 你要安装的linux系统的大小

5. 生成BOOT.BIN

boot.bin文件包括:

| 包含的文件 | 解释 |

|---|---|

| FSBL | |

| bitstream | 配置PL端的程序,可选,如果需要使用显示器输出,则必须。 |

| SSBL | 这里使用uboot |

5.1 FSBL制作

打开vivado 2016.4 ,新建项目,选择zedboard zynq evaluation and development Kit。(全文没有重点指出的操作和设置,均为default即可)

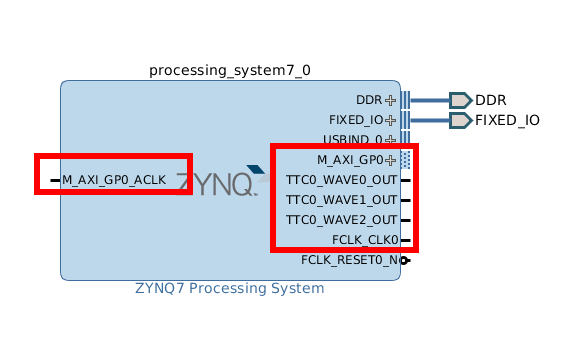

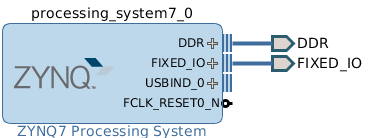

先新建一个Block Design(左边Project Manager--》IP integrator--》create Block design),在Diagram视图中add IP。输入zynq选择唯一的 zynq7 process system,并点击上方的“Run Block automation”,

双击生成的:

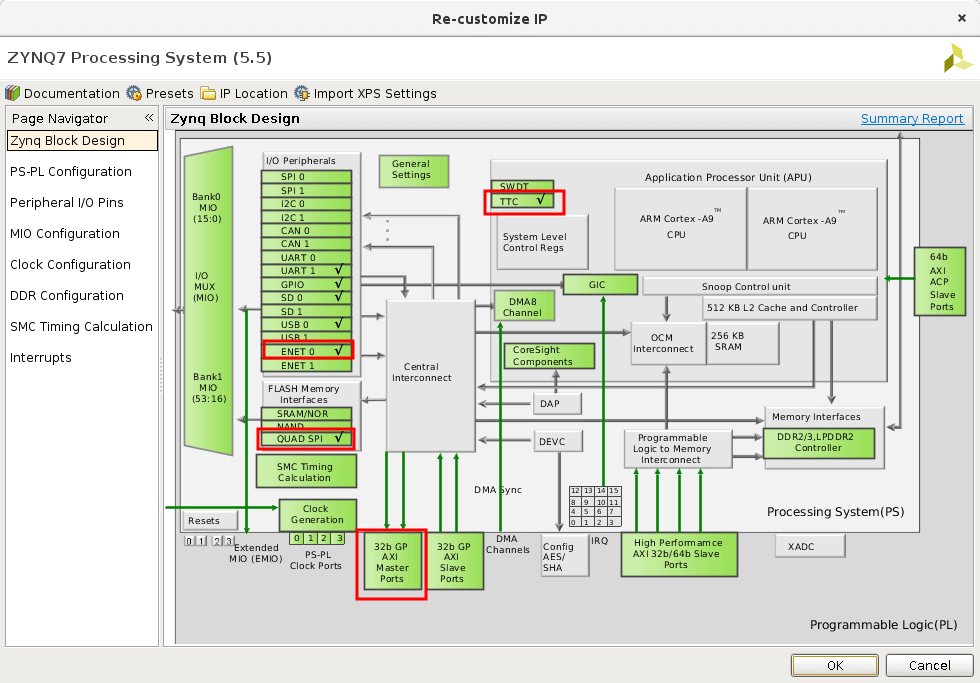

弹出Re-customize IP窗口,上图红色圈中是我们需要取消的引脚。

从Clock Configuration中展开PL Fabric Clocks,取消FCLK_CLK0,确认之后,会发现上图中的FCLK_CLK0消失。

对于其他,以取消TTC为例,从Zynq Block Design中点击TTC,会自动跳转到对应的详细设计部分,取消勾选,再切换回zynq block design,取消掉其他红框里的内容,点击OK完成。

可以右键--》regenerate layout,自动调整下布局,则会变成下图的样子:

回到Block Design的sources视图,在System上右键选择Create HDL Wrapper。完成后点击左边Flow Navigator中的Generate BitStream。等待Vivado完成综合、实现、生成bitstream,右上角有进度,时间比较长。

点击File->Export->ExportHardware,勾选include bitstream,确认后点击File->Launch SDK,系统会自动开启SDK软件

在SDK中点击菜单File->New->Application Project。项目名fsbl(可以更改),OS平台standalone,语言为C,点击Next,Templates选项选择ZynqFSBL。

点击Finish,SDK会自动编译FSBL代码,并在工程Debug下生成fsbl.elf目标文件。Project Explorer --》binaries--》fsbl.elf。

5.2 编译Uboot

建议直接从release里选择版本,此处选择了xilinx-v2016.4。下载,解压出来。

设置环境变量,实际上新版本的vivado已经包含了xilinx-arm toolchain,因此只需要使用vivado目录下的环境变量设置脚本,即可使用arm-xilinx-*工具

# 你的vivado地址

source ~/d/fpga/Vivado/2016.4/settings64.sh

export CROSS_COMPILE=arm-xilinx-linux-gnueabi-

修改include/configs/zynq_common.h中sdboot数据,让我们的u-boot在启动的时候不会试图去加载ramdisk image(这一步可选):

"sdboot=if mmcinfo; then " \

"run uenvboot; "\

"echo Copying Linuxfrom SD to RAM... && " \

"load mmc 0${kernel_load_address} ${kernel_image} && " \

"load mmc 0${devicetree_load_address} ${devicetree_image} && " \

"bootm${kernel_load_address} - ${devicetree_load_address} ; " \

生成zedboard配置文件并编译uboot

make ARCH=arm CROSS_COMPILE=arm-xilinx-linux-gnueabi- zynq_zed_config

make ARCH=arm CROSS_COMPILE=arm-xilinx-linux-gnueabi-

将得到的可执行文件u-boot修改为elf格式

mv u-boot u-boot.elf

5.3 生成BOOT.BIN

打开xilinx SDK,菜单Xilinx Tools--》Create Boot Image。

设置BIF文件路径(BIF文件用于指定当前boot.bin制作过程中用到的三个文件的路径,相当于一个项目配置文件),然后在下方的配置里按照顺序添加如下文件

- FSBL文件,默认在

你的项目路径/项目名.sdk/fsbl/Debug/fsbl.elf,添加后,会自动识别分区格式为bootloader, - bitstream文件,从vivado,File--》Export--》export bitstream file,保存到你想保存的位置,然后同FSBL文件一样,添加上,会自动识别分区格式为datafile。

- uboot文件,就是上一步编译出的

u-boot.elf文件,同样添加上。

点击Create Image创建boot.bin,成功的话会在输出路径生成相应文件。

在sdk 底部的console会有个错误输出awk: symbol lookup error: awk: undefined symbol: mpfr_z_sub但是文件正常生成了,而且运行没有问题。不清楚这个错误有什么问题。

6. 编译内核和设备树

6.1 编译内核

从xilinx 提供的官方linux kernel的release下载,不要git clone(或者clone时添加--depth=1来限制拉取的commit记录),否则文件夹会很大。

解压出来,配置编译环境、内核参数,并编译内核:

export ARCH=arm

export CROSS_COMPILE=arm-xilinx-linux-gnueabi-

# 安装uboot工具

sudo apt-get install u-boot-tools

make xilinx_zynq_defconfig

make uImage LOADADDR=0x00008000

注意:如果你的系统比较新,那么openssl库应该是1.1,由于openssl库升级的缘故,在编译现有的xilinx linux kernel时,会出现:

cpp error: dereferencing pointer to incomplete type ‘RSA {aka struct rsa_st}’ if (BN_num_bits(key->e) > 64)的错误。现在xilinx官方邮件列表正在讨论这个问题。截止2017.4.7,尚未merge补丁。

所以需要将你本地的openssl库降级成1.0:

shell sudo apt-get install libssl1.0-dev会自动卸载当前最新的版本1.1。

6.2 编译devicetree

设备树devicetree, 也称作Open Firmware(OF)或FlattenedDevice Tree(FDT)。本质上是一个字节码格式的数据结构,其中包含信息在内核启动时非常有用。bootloader在跳到内核入口点之前将这一块数据复制到RAM中的已知地址。

修改arch/arm/boot/dts/zynq-zed.dts文件:

chosen {

# 默认bootargs是空的字符串,填充如下数据

bootargs ="console=ttyPS0,115200 root=/dev/mmcblk0p2 rw earlyprintk rootfstype=ext4 rootwait devtmpfs.mount=0";

stdout-path = "serial0:115200n8";

};

表示root目录在sd卡的第二个分区。

cd 到arch/arm/boot/dts/,执行:

~/d/fpga/make_boot/linux-xlnx-xilinx-v2016.4/scripts/dtc/dtc –I dts –O dtb -o ../../../devicetree.dtb ./zynq-zed.dts

dtc是xilinx官方kernel里带的一个工具,-I dts表示输入格式是dtc,-O dtb表示输出格式是dtb,-o表示生成的dtb放哪里,最后是输入文件的位置。注意一定要先cd到dts文件所在目录,因为它引用了当前目录下别的文件。

7. linaro ubuntu

从linaro发行版官网下载ubuntu images developer版本或者其他版本,解压出下载的压缩包(网上有些文章用的是老版本的包,系统在binary/boot/filesystem.dir),将加压出的内容拷贝到sd卡第二个分区。

cd binary

# 我的自动挂载点是/media/find/root

sudo rsync -a ./* /media/find/root/

# 卸载,一定要等待写入结束

sudo umount /media/find/root

sudo umount /media/find/boot

8. 启动

将sd卡插好,usb 连接到PC,打开zedboard开关,PC上打开命令行,使用minicom连接。

8.1 minicom设置

sudo minicom -s

# 选择serial port setup,并设置 串口设备为 ttyACM0

A - Serial Device : /dev/ttyACM0

# 确认 bps之类如下,波特率选为115200 8N1(数据位8,奇偶校验无,停止位1),

E - Bps/Par/Bits : 115200 8N1

配置完成后,可通过sudo minicom连接设备

8.2 启动root分区的linaro ubuntu 系统

由于之前我们已经修改了bootargs,因此这里可以直接通过boot命令启动。

9. REV-D板子无法显示图形界面

尚未解决

Reference

Zedboard上运行Linaro系统(二):生成BOOT.BIN

Comments